Cache do processador

Cache do processador

| Modelo | Cache , memória de armazenamento , memória volátil |

|---|

| Precedido por | Registro do processador |

|---|

| Seguido pela | Memória do computador ( in ) |

|---|

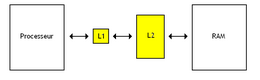

Um cache de processador é um cache de hardware usado pela unidade de processamento central (CPU) de um computador para reduzir o custo médio (tempo ou energia) de acesso aos dados na memória principal . Um cache de processador é uma memória menor e mais rápida, localizada mais próxima de uma unidade de processamento central (ou núcleo do microprocessador ), que armazena cópias de dados de locais da memória principal que são frequentemente usados antes de sua transmissão para os registros do processador . A maioria das CPUs tem diferentes caches independentes, incluindo caches de instrução e dados, onde o cache de dados é geralmente organizado como uma hierarquia de vários níveis de cache (L1, L2, L3, L4, etc.). Os caches do processador são uma parte da memória principal, assim como os registros do processador e a memória principal, eles são essenciais para o funcionamento do computador.

Todos os processadores modernos (rápidos), com algumas exceções, têm vários níveis de caches de processador. Os primeiros processadores que usavam cache tinham apenas um nível de cache; ao contrário de caches de nível superior posteriores, ele não foi dividido em L1d (para dados) e L1i (para instruções). Quase todas as CPUs atuais com caches têm um cache L1 dividido. Eles também têm caches L2 e para processadores maiores, caches L3 também. O cache L2 normalmente não é dividido e atua como um repositório comum para o cache L1 já dividido. Cada núcleo de um microprocessador multi-core tem um cache L1 dedicado e normalmente não é compartilhado entre os núcleos. O cache L2 e os caches de nível superior podem ser compartilhados entre os núcleos. De cache L4 é atualmente rara e é normalmente encontrado em algum tipo de memória de acesso aleatório dinâmico (DRAM), ao invés de estática de acesso aleatório memória de acesso aleatório (SRAM), em um circuito integrado morrer ou separada microchip (excepcionalmente, um eDRAM tipo de cache lata ser usado para todos os níveis de cache, até L1). Historicamente, este também foi o caso com o cache L1, onde chips maiores permitiram sua integração e geralmente em todos os níveis de cache, exceto talvez o último nível. Cada nível adicional de cache é otimizado de maneira diferente e tende a ser maior que o anterior.

Existem outros tipos de caches, como o buffer de tradução (TLB), que faz parte da unidade de gerenciamento de memória (MMU) e que é adequado para a maioria das CPUs.

Notas e referências

- (fr) Este artigo foi retirado parcial ou totalmente do artigo da Wikipedia em inglês intitulado " CPU cache " ( veja a lista de autores ) .

- Franck Delattre, " L'architecture Intel Nehalem " , em hardware.fr , BeHardware ,17 de setembro de 2008(acessado em 29 de janeiro de 2020 )